# Lecture Notes in Computer Science

5047

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

**David Hutchison**

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Kenji Suzuki Teruo Higashino Andreas Ulrich Toru Hasegawa (Eds.)

# Testing of Software and Communicating Systems

20th IFIP TC 6/WG 6.1 International Conference, TestCom 2008 8th International Workshop, FATES 2008 Tokyo, Japan, June 10-13, 2008 Proceedings

#### Volume Editors

Kenji Suzuki The University of Electro-Communications Tokyo 182-8585, Japan E-mail: suzuki@cs.uec.ac.jp

Teruo Higashino Osaka University Department of Information Networking Osaka 565-0871, Japan E-mail: higashino@ist.osaka-u.ac.jp

Andreas Ulrich

Siemens AG, Corporate Research & Technologies CT SE 1

81730 Munich, Germany

E-mail: andreas.ulrich@siemens.com

Toru Hasegawa KDDI R&D Laboratories Inc. Saitama 356-8502, Japan E-mail: hasegawa@kddilabs.jp

Library of Congress Control Number: 2008927735

CR Subject Classification (1998): D.2.5, D.2-3, C.2, F.3, K.6

LNCS Sublibrary: SL 2 – Programming and Software Engineering

ISSN 0302-9743

ISBN-10 3-540-68514-6 Springer Berlin Heidelberg New York ISBN-13 978-3-540-68514-2 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© IFIP International Federation for Information Processing 2008 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12273713 06/3180 5 4 3 2 1 0

# **Preface**

This volume contains the proceedings of TESTCOM/FATES 2008, a joint conference of two communities: TESTCOM was the 20th edition of the IFIP TC6/WG6.1 International Conference on Testing of Communicating Systems and FATES was the 8th edition of the International Workshop on Formal Approaches to Testing of Software. TESTCOM/FATES 2008 was held at the Campus Innovation Center in Tokyo, Japan during June 10–13, 2008.

Testing is one of the most important techniques for validating and checking the correctness of communication and software systems. Testing, however, is also a laborious and very cost-intensive task during the development process of such systems. TESTCOM is a series of international conferences addressing the problems of testing communicating systems, including communication protocols, services, distributed platforms, and middleware. FATES is a series of international workshops discussing the challenges of using rigorous and formal methods for testing software systems in general. TESTCOM/FATES aims at being a forum for researchers, developers, and testers to review, discuss, and learn about new approaches, concepts, theories, methodologies, tools, and experiences in the field of testing of communicating systems and software.

TESTCOM has a long history. Previously it was called the International Workshop on Protocol Test Systems (IWPTS) and changed its name to the International Workshop on Testing of Communicating System (IWTCS) later. The previous conferences were held in Vancouver, Canada (1988); Berlin, Germany (1989); McLean, USA (1990); Leidschendam, The Netherlands (1991); Montréal, Canada (1992); Pau, France (1993); Tokyo, Japan (1994); Evry, France (1995); Darmstadt, Germany (1996); Cheju Island, Korea (1997); Tomsk, Russia (1998); Budapest, Hungary (1999); Ottawa, Canada (2000); Berlin, Germany (2001); Sophia Antipolis, France (2002); Oxford, UK (2004); Montréal, Canada (2005); New York, USA (2006) and Tallinn, Estonia (2007).

FATES also has its history. The previous workshops were held in Aalborg, Denmark (2001); Brno, Czech Republic (2002); Montréal, Canada (2003); Linz, Austria (2004); Edinburgh, UK (2005); Seattle, USA (2006), and Tallinn, Estonia (2007). TESTCOM and FATES became a joint conference in 2007.

In addition, FORTE 2008, the 28th IFIP International Conference on Formal Methods for Networked and Distributed Systems, was also held at the same place and time, as it did last year. Thus, the co-location of TESTCOM/FATES and FORTE fostered the collaboration between different communities. The common spirit of both conferences was underpinned by joint opening and closing sessions, invited talks, as well as joint social events.

TESTCOM/FATES received a reasonable number of submissions this year. Initially 58 abstracts were submitted, from which 42 research full papers were elaborated. The Program Committee finally selected 18 papers for presentation at the

#### VI Preface

conference. Together with the invited presentations by Yutaka Yasuda from KDDI Corporation, Japan, and Paul Baker from Motorola, UK, they formed the contents of the proceedings. In addition, the conference contained another invited presentation on behalf of FORTE by Wolfram Schulte from Microsoft Research, USA. Moreover, presentations on industrial best practices and work-in-progress presentations rounded off the conference. A tutorial day preceded the conference.

It took tremendous efforts to organize this event. We would like to thank all the contributors for the success of TESTCOM/FATES 2008. In particular we are grateful to the Steering Committee of IFIP TESTCOM, the Program Committee, and all reviewers for their support in selecting papers of high quality. Without these contributions, these proceedings would not exist. We thank the International Communications Foundation, Support Center for Advanced Telecommunications Technology Research, Foundation, Microsoft Research, and KDDI Corporation for their financial support and Springer for publishing the proceedings. Last but not least, we would also like to express our thanks to the members of the Local Arrangements team from KDDI R&D Laboratories Inc., The University of Electro-Communications, Osaka University, and the Nara Institute of Science and Technology for their continuous support of this conference.

March 2008

Kenji Suzuki Teruo Higashino Andreas Ulrich Toru Hasegawa

# Conference Organization

#### General Chairs

Kenji Suzuki (The University of Electro-Communications, Japan) Teruo Higashino (Osaka University, Japan)

## **Program Chairs**

Andreas Ulrich (Siemens AG, Corporate Technology, Germany) Toru Hasegawa (KDDI R&D Laboratories Inc., Japan)

# **TESTCOM Steering Committee**

John Derrick (Chairman, University of Sheffield, UK)

Ana R. Cavalli (INT, France)

Roland Groz (Grenoble Institute of Technology, France)

Alexandre Petrenko (CRIM, Canada)

# **Program Committee**

Bernhard K. Aichernig (TU Graz, Austria)

Antonia Bertolino (ISTI-CNR, Italy)

Gregor v. Bochmann (University of Ottawa, Canada)

Richard Castanet (LABRI, France)

Shing Chi Cheung (Hong Kong University of Science and Technology, China)

Sarolta Dibuz (Ericsson, Hungary)

Rachida Dssouli (Concordia University, Canada)

Khaled El-Fakih (American University of Sharjah, UAE)

Marie-Claude Gaudel (University of Paris-Sud, France)

Jens Grabowski (University of Göttingen, Germany)

Rob Hierons (Brunel University, UK)

Dieter Hogrefe (University of Göttingen, Germany)

Antti Huima (Conformiq Software Ltd., Finland)

Thierry Jéron (IRISA Rennes, France)

Ferhat Khendek (Concordia University, Canada)

Myungchul Kim (ICU, Korea)

Yoshihi Kinoshita (AIST, Japan)

Hartmut König (BTU Cottbus, Germany)

Victor V. Kuliamin (ISP RAS, Russia)

David Lee (Ohio State University, USA)

#### VIII Organization

Bruno Legeard (Leirios, France)

Giulio Maggiore (Telecom Italia Mobile, Italy)

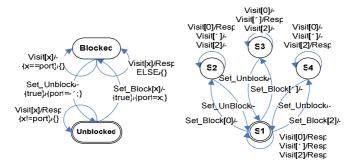

José Carlos Maldonado (University of San Carlos, Brazil)

Brian Nielsen (University of Aalborg, Denmark)

Manuel Núñez (Universidad Complutense de Madrid, Spain)

Tomohiko Ogishi (KDDI R&D Laboratories Inc., Japan)

Ian Oliver (Nokia Research, Finland)

Doron Peled (University of Bar-Ilan, Israel)

Fumiaki Sato (Toho University, Japan)

Ina Schieferdecker (Fraunhofer FOKUS, Germany)

Jan Tretmans (Embedded Systems Institute, The Netherlands)

Hasan Ural (University of Ottawa, Canada)

Mark Utting (University of Waikato, New Zealand)

M. Umit Uyar (City University of New York, USA)

Margus Veanes (Microsoft Research, USA)

César Viho (IRISA Rennes, France)

Carsten Weise (RWTH Aachen, Germany)

Colin Willcock (Nokia Siemens Network, Germany)

Burkhart Wolff (ETH Zurich, Switzerland)

Nina Yevtushenko (Tomsk State University, Russia)

#### **Local Organization**

Tomohiko Ogishi (Chair, KDDI R&D Laboratories Inc.) Takaaki Umedu (Osaka University)

#### Additional Reviewers

Andreas Griesmayer

Maxim Gromov

Tatsuya Abe Jiale Huo Soonuk Seol César Andrés Adenilso da Silva Simão Iksoon Hwang Gabor Batori Sungwon Kang Simone R.S. Souza Sergiv Boroday Zhifeng Lai Toshinori Takai Ferenc Bozoki Wissam Mallouli Erik Tschinkel Patryk Chamuczynski Mercedes G. Merayo Yu Wang Laurent Mounier Hiroshi Watanabe Vianney Darmaillacq Thomas Deiß Masahiro Nakano Bachar Wehbi Alexandra Desmoulin Helmut Neukirchen Martin Weiglhofer Rita Dorofeeva T.H. Ng Chunyang Ye Levente Eros Svetlana Prokopenko Benjamin Zeiß

Ismael Rodriguez

Rudolf Schlatte

# **Sponsoring Institutions**

International Communications Foundation, Tokyo, Japan Support Center for Advanced Telecommunications Technology Research, Foundation, Tokyo, Japan Microsoft Research, Redmond, USA KDDI Corporation, Tokyo, Japan

# Table of Contents

| Invited Talks                                                                                                                |     |

|------------------------------------------------------------------------------------------------------------------------------|-----|

| All-IP Based Ultra 3G Network/Service Development in a Competitive Market                                                    | 1   |

| Models and Testing – A Recipe for Improved Effectiveness?                                                                    | 5   |

| General Software Testing                                                                                                     |     |

| Runtime Verification of C Programs                                                                                           | 7   |

| Test Construction for Mathematical Functions                                                                                 | 23  |

| Model-Based Testing Service on the Web                                                                                       | 38  |

| Testing Continuous and Real-Time Systems                                                                                     |     |

| Using Disparity to Enhance Test Generation for Hybrid Systems                                                                | 54  |

| Modeling Property Based Stream Templates with TTCN-3 Juergen Grossmann, Ina Schieferdecker, and Hans-Werner Wiesbrock        | 70  |

| THOTL: A Timed Extension of HOTL                                                                                             | 86  |

| Network Testing                                                                                                              |     |

| Model-Based Firewall Conformance Testing                                                                                     | 103 |

| VCSTC: Virtual Cyber Security Testing Capability – An Application<br>Oriented Paradigm for Network Infrastructure Protection | 119 |

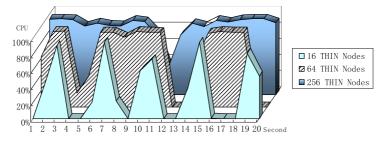

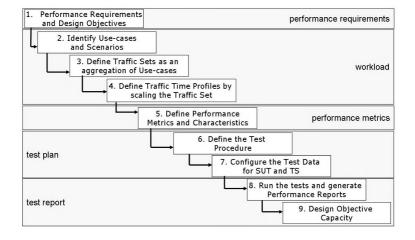

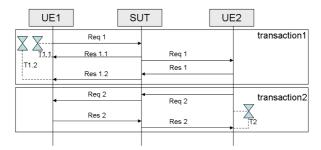

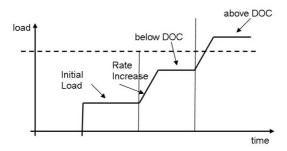

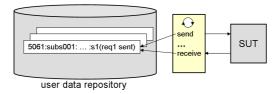

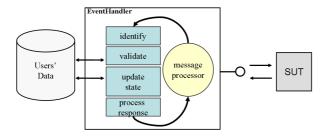

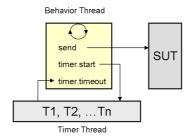

| Performance Test Design Process and Its Implementation Patterns for Multi-services Systems                                              | 135 |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Test Generation                                                                                                                         |     |

| Generating Checking Sequences for Partial Reduced Finite State  Machines                                                                | 153 |

| Testing Systems Specified as Partial Order Input/Output Automata  Gregor v. Bochmann, Stefan Haar, Claude Jard, and Guy-Vincent Jourdan | 169 |

| Test Purpose Concretization through Symbolic Action Refinement Alain Faivre, Christophe Gaston, Pascale Le Gall, and Assia Touil        | 184 |

| Concurrent System Testing                                                                                                               |     |

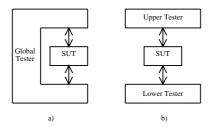

| Implementation Relations for the Distributed Test Architecture                                                                          | 200 |

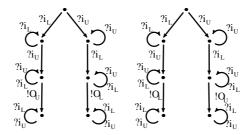

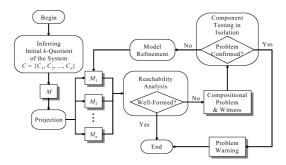

| Modular System Verification by Inference, Testing and Reachability Analysis                                                             | 216 |

| Test Plan Generation for Concurrent Real-Time Systems Based on<br>Zone Coverage Analysis                                                | 234 |

| Applications of Testing                                                                                                                 |     |

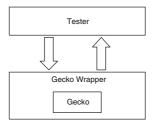

| Applying Model-Based Testing to HTML Rendering Engines – A Case Study                                                                   | 250 |

| Model-Based Generation of Testbeds for Web Services                                                                                     | 266 |

| Real-Time Testing with TTCN-3                                                                                                           | 283 |

| Author Index                                                                                                                            | 303 |

# All-IP Based Ultra 3G Network/Service Development in a Competitive Market

#### Yutaka Yasuda

KDDI Corporation 3-10-10, Iidabashi, Chiyoda-ku, Tokyo, Japan

**Abstract.** FMC (Fixed Mobile Convergence) is a key concept of NGN (Next generation Network) and KDDI announced the Ultra 3G concept based on all-IP network configuration, 3 years ago. Now, the Ultra 3G concept has evolved toward FMBC (Fixed Mobile Broadcast Convergence). This talk introduces how KDDI has been swiftly and reliably developing all-IP based networks and FMBC services.

Keywords: All-IP Networks, FMBC, Modular Development.

#### 1 Introduction

Recently, telecommunication carriers have considered that convergence of fixed and mobile communications, known as FMC (Fixed Mobile Communication) to be a key in creating new services and increasing the market. KDDI, a telecommunication carrier in Japan, has provided various kinds of FMC services such as "LISMO", a comprehensive music service that links "auc mobile phones with PCs (January 2006). In the future, KDDI will continue to meet customer demands by creating more convenient and attractive services and content along with the business strategy of "Fixed Mobile and Broadcast Convergence (FMBC)", targeting a fusion among fixed and mobile communications and broadcasting.

Within the competitive market in Japan, it is important to realize rapid and reliable developments of FMBC networks/services. After introducing the Ultra 3G concept, this invited talk describes how KDDI has been achieving rapid and reliable developments especially for FMBC services, before subsequently concluding with details of how KDDI provides reliability after developments.

# 2 The Ultra 3G Concept

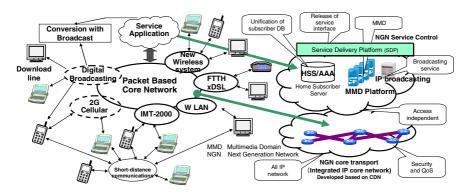

Based on Ultra 3G, a next generation communication infrastructure concept, KDDI aims to build a fixed-mobile integrated network which provides integrated services, including third generation mobile phone systems such as "EV-DO Rev.A" (launched in December 2006), wireless LAN, new wireless systems such as mobile WiMAX and beyond 3G mobile network, and wired accesses such as ADSL and FTTH (Hi-kari-One). The concept is illustrated in Fig. 1. A service control system will be developed to provide seamless services with various forms of access means complementing

each other. This system will be constructed in compliance with IP Multimedia Subsystem (IMS)/Multimedia Domain (MMD), which are standardized by 3GPP and 3GPP2, and expected to be globally deployed in the future.

This future infrastructure will enable customers to enjoy high-speed data services and high-quality multimedia services anytime and anywhere, within an optimum communication environment, without being aware of differences between fixed and mobile communications.

Fig. 1. Ultra 3 G Concept

# 3 Development Policies and Practices

There are two important issues relating to network and service developments, respectively. The first concerns the reliability of all-IP networks compared to the circuit based legacy network. Legacy SS7 protocol suites are designed to achieve its reliability with coordination between protocol layers, while conversely, IP technology on which VoIP (Voice over IP) is based is relatively independent from both upper and lower layers. This is clearly one of the advantages of IP technology, but, at the same time, needs some additional knowledge and operational skills to achieve the same level of reliability. Also, VoIP networks are more centralized compared to the legacy equivalents, meaning that one problem may have a wider impact on the entire network. The KDDI VoIP system has improved through experiences over the years.

The second issue is rapid service development. The competitive market demands the rapidity of FMBC network/service developments without any loss of reliability. The left of this section shows some recent KDDI practices to introduce modular development to software systems comprising services rapidly and reliably delivered.

#### 3.1 Common Platform for Cellular Phone Software

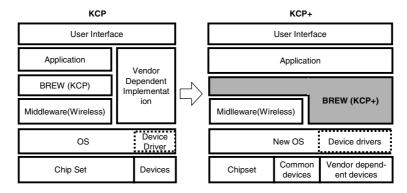

KDDI cellular phone consists of chipsets provided by QUALCOMM and other peripheral devices. In order to achieve portability of application programs on them, KDDI has been engaged in creating a common platform, KCP (KDDI Common Platform), as shown in the left part of Fig. 2. But due to device specific interfaces, vendor dependent implementations still existed and as the result application program developments were

time consuming and were error prone. In order to achieve more portability, KDDI extended it to the more modular platform, KCP+, as shown in the right part of Fig. 2. KCP+ is developed on MSM7500<sup>TM</sup> and BREW¹ which are the chipset and its application programming interface respectively. It makes all kinds of programs common to any cellular phones. These include not only application programs such as browsers, mailers but also middleware software and OS (Operating System) itself.

Providing KCP+ to vendors is expected to slash the development time and costs are expected to be reduced drastically. Besides vendors can also devote themselves to implementing their own functions related to UI (user interface) and/or design, etc. that differentiate their cellular phones to those of other vendors.

Fig. 2. Common Platform for Cellular Phone Software

#### 3.2 SOA Based Development

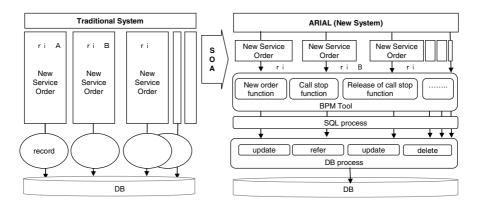

BSSs (Business Support Systems) such as service, business and billing management systems used to be independently developed for individual services. Before the FMBC era, this style was not a problem; however, during the FMBC era, dependency among program modules of different BSSs has become problematic. Many new developments and updates which are performed due to rapidly changing business environments make them time consuming and error-prone, because a single change of an FMBC service has effects on several program modules of several BSSs. One possible solution is the introduction of an SOA (Service Oriented Architecture) based development.

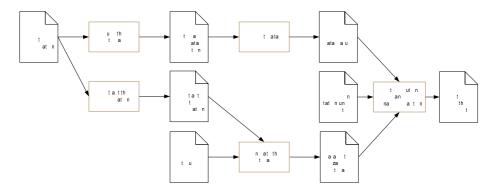

As the initial step, KDDI has developed a BSS system that provides service management for Internet services over cellular phone networks. Before the system, known as ARIAL, was developed, service management systems were developed for individual services as shown in the left of Fig. 3. Conversely, functions common to all services such as "new order processes" and "call stop processes" are modeled as services of SOA-based development and are implemented in modular fashion using a BPM (Business Process Management) tool as shown in the right part of Fig.3. By introducing modular developments, a saving around 30% of the development time is possible while the throughput becomes 1.5 times as high as the previous BSS. Besides, failures that are localized to specific functions also improve reliability.

<sup>&</sup>lt;sup>1</sup> BREW and MSM7500<sup>TM</sup> are trademarks of QUALCOMM.

Fig. 3. SOA based Development

#### 4 Conclusion

KDDI has been introducing FMBC core networks based on the Ultra 3G concept and FMBC services not only to survive the competitive environment, but also to enrich daily lives in Japan. This extended abstract shows the recent software development practices of KDDI. In addition KDDI is devoting itself to achieve flexible operations after developing FMBC network/service. The following are recent examples of techniques achieving flexible operations.

- Over-the-air software download techniques that distribute amendment of software bug and/or new software updates to cellular phones.

- Software-based device management techniques that collect and diagnose remote cellular phone logs.

- SLM (Service Level Management) techniques that measure the actively response times of servers and network equipments comprising services.

- Software radio techniques that enable programmability in wireless signal processing and reuse techniques that enable the software implementations of some wireless programmable devices to be ported to others at reasonable costs.

# Models and Testing – A Recipe for Improved Effectiveness?

#### Paul Baker

Motorola Ltd.

Motorola's Corporate Software Excellence Team

Basingstoke, Hampshire, RG22 4PD, United Kingdom

Paul.Baker@motorola.com

**Abstract.** In an ongoing effort to reduce development costs in spite of increasing system complexity, Motorola has been a long-time adopter of Model-Driven Engineering practices. The foundation of this approach is the creation of rigorous models throughout the development process, thereby, enabling the introduction of automation into the development life cycle and supporting frameworks.

#### 1 Introduction

In this talk we present Motorola's experiences over the past 15 years in using models [1][2] to improve testing effectiveness from defect prevention through to test configuration. We present the motivation(s) for using models and in particular their impact on product testing and quality. Specifically, we present and discuss cases and metrics where models have been used for:

- Defect Prevention. We present the approaches that have been employed for the early discovery of defects through the application of requirements verification techniques and the lessons learnt from doing so. In addition, we introduce recent work on trying to fix identified defects automatically through the application of inference [3][4][5];

- Early testing of designs through the use of co-simulation, as well as, experiences from previous usage of formal verification techniques[6];

- Aiding test development and reuse. In this case we discuss some of the issues encountered during general test development and elaborate why modeling concepts are useful in overcoming some of these obstacles [7];

- Enabling test generation and automation. It is well understood that models can lend themselves to test generation. We present some of the issues learnt and also their application within the context of existing modeling and test standards, such as UML, TTCN-3, MSC etc.;

- *Model-driven testability*. Here we introduce recent work on using models for the systematic understanding of testability concerns [8], which are crucial for cost effective test automation.

We also present lessons learnt from deploying model-related technologies and the different business strategies that have been used to effect their deployment, e.g. maturity models, aspects, and services. In doing so, we discuss the lessons learnt and directions/challenges moving forward with the perspective of a large testing technology portfolio.

#### References

- [1] Baker, P., Loh, S., Weil, F.: Model-Driven Engineering in a Large Industrial Context Motorola Case Study. In: Briand, L.C., Williams, C. (eds.) MoDELS 2005. LNCS, vol. 3713, pp. 476–491. Springer, Heidelberg (2005)

- [2] Weigert, T., Weil, F., Marth, K., Baker, P., Jervis, C., Dietz, P., Gui, Y., Van de Berg, A., Fleer, K., Nelson, D., Wells, M., Mastenbrook, B.: Experiences in Deploying Model-Driven Engineering. In: Gaudin, E., Najm, E., Reed, R. (eds.) SDL 2007. LNCS, vol. 4745, Springer, Heidelberg (2007)

- [3] Baker, P., Bristow, P., Burton, S., King, D., Jervis, C., Mitchell, B., Thomson, R.: Detecting and Resolving Semantic Pathologies in UML Sequence Diagrams. In: Joint 10th European Software Engineering Conference and 13th ACM SIGSOFT Symposium on the Foundations of Software Engineering, Lisbon, September 2005, pp. 50–59 (2005)

- [4] Mitchell, B.: Resolving Race Conditions in Asynchronous Partial Order Scenarios. IEEE Transactions on Software Engineering, TSE-0039-0205 31(9), 767–784 (2005)

- [5] Baranov, S., Jervis, C., Kotlyarov, V., Letichevsky, A., Weigert, T.: UML for Real Design of Embedded Real-Time Systems, pp. 323–342 ISBN 978-1-4020-7501-8

- [6] Baker, P., Jervis, C.: Early UML Model Testing using TTCN-3 and the UML Testing Profile. In: TAICPART: Testing, Academic, and Industrial Conference, Practice and Research, IEEE Computer Society Press, Los Alamitos ISBN 0-7695-2984-4

- [7] Baker, P., Dai, Z.R., Grabowski, J., Haugen, O., Schieferdecker, I., Williams, C.E.: Model-Driven Testing Using the UML Testing Profile. Springer, Heidelberg (2007)

- [8] Baker, P., Jervis, C.: Early Model Testing and Testability Analysis using UML. Software Testing, Verification and Reliability (STVR) (submitted)

# **Runtime Verification of C Programs**

Klaus Havelund

Jet Propulsion Laboratory California Institute of Technology Pasadena CA 91109, USA Klaus.Havelund@jpl.nasa.gov

**Abstract.** We present in this paper a framework, RMOR, for monitoring the execution of C programs against state machines, expressed in a textual (nongraphical) format in files separate from the program. The state machine language has been inspired by a graphical state machine language RCAT recently developed at the Jet Propulsion Laboratory, as an alternative to using Linear Temporal Logic (LTL) for requirements capture. Transitions between states are labeled with abstract event names and Boolean expressions over such. The abstract events are connected to code fragments using an aspect-oriented pointcut language similar to ASPECTJ's or ASPECTC's pointcut language. The system is implemented in the C analysis and transformation package CIL, and is programmed in OCAML, the implementation language of CIL. The work is closely related to the notion of stateful aspects within aspect-oriented programming, where pointcut languages are extended with temporal assertions over the execution trace.

#### 1 Introduction

The field of program verification is concerned with the problem of determining whether a program conforms to a specification. The pure verification problem consists of proving that all possible executions of the program conform to the specification. This is in general undecidable. Runtime verification is a less ambitious, but more feasible approach, just attempting to prove conformance of a single execution wrt. a specification. The specification can in this context be seen as a formalized oracle that can be used during testing, or it can become part of a fault protection system that runs in tandem with the program during its deployment, while triggering error correction code when non-conformance to the specification is detected.

The paper presents the runtime verification framework, RMOR (Requirement Monitoring and Recovery, pronounced "armor"), for monitoring C programs against state machines, using an aspect-oriented pointcut language to perform program instrumentation and connect the abstract events occurring in state machines with code fragments. The work has been partly driven by the context of embedded systems for planetary rovers and unmanned deep-space spacecraft as developed at NASA's Jet Propulsion Laboratory (JPL), where the majority of such code is written in C. The work presented reflects the following four observations. First, state machines appear a natural notation for programmers to apply, in contrast to for example temporal logic, or even regular expressions. Regular expressions are likely the most attractive of the succinct notations,

but seem to be best suited for specifying "small" properties, whereas state machines support "big" properties involving many states. Second, although graphical editors for state machines are convenient, many programmers find textual programming-like notations convenient. Third, program instrumentation should be automated, connecting events to program points. Aspect-oriented programming has offered powerful pointcut languages for expressing such instrumentation. Fourth, most runtime verfication environments to date have been developed for Java, and C has been somewhat ignored. This is unfortunate since a majority of embedded software is written in C.

The RMOR language has inspirations from several sources. The language supports a notion of state machines directly influenced by RCAT (Requirement CApture Tool), a graphical state machine language language and editor [24,25]. That graphical state machine language is inspired by Linear Temporal Logic (LTL) and allows for liveness properties to be stated as well as safety properties. This is achieved by introducing special *error states* and *liveness states*. RCAT was developed to support property specification for the SPIN model checker [17]<sup>1</sup> and was together with RMOR products of the *Reliable Software Systems Development* (RSSD) project, funded by NASA. Beyond RCAT, another direct inspiration has been the STATL specification language [12], from where a distinction between *consuming* and *non-consuming* transitions was borrowed (a consuming transition leaves the source state, whereas a non-consuming leaves a "token" – does not consume the token – in the source state when the transition is taken). Finally aspectoriented programming, and specifically ASPECTJ [18] has strongly inspired the pointcut language driving program instrumentation. More recently, ASPECTC [2] has emerged as an aspect-oriented framework for C. This will be discussed further in Section 7.

A considerable amount of research has been invested in program monitoring systems by different communities within the last 5-10 years. The runtime verification community is concerned with program correctness [10,19,13,26,11,8]. This includes our own work [15,16,4]. Most of these efforts investigate more or less powerful temporal logics, with an exception in [11], which suggests the use of graphical UML state charts. The aspect-oriented programming community is investigating what is referred to as stateful aspects, where the pointcut language is extended with dynamic trace predicates [9,29,7,28,1]. These pieces of work are often extensions of ASPECTJ [18]. TRACE-MATHCES [1] for example is an extension of ASPECTJ with regular expressions. JASCO [28] is a state machine solution for Java. An exception is ARACHNE [9], which performs runtime weaving into binary code of C programs. ARACHNE supports a form of trace predicates describing sequences of function calls, a limited form of regular expressions. The SLIC language [3] of the SLAM project is a specification language for C much resembling an aspect-oriented programming language, but simplified to support static verification as well as monitoring. The language supports state variables as well as access to function arguments and return values, but state machines have to be encoded using enum types, and the event language is not as comprehensive as a general purpose pointcut language. The program analysis community has also contributed to this field [20] and the model checking community, which uses timed automata for testing, including monitoring [27,6].

<sup>&</sup>lt;sup>1</sup> RCAT automata are by the RCAT tool translated into Büchi automata. RMOR can specifically monitor against such Büchi automata, although this is not the main purpose of the tool.

Our contributions to these efforts are: (i) to suggest a simple and natural textual programming notation for non-deterministic state machines integrated with an aspect-oriented pointcut language for program monitoring. This includes adapting the notions of error and live states from RCAT [24] for monitoring. With these concepts simple (finite trace) LTL properties can be stated naturally as state machines (the contribution of [24]) and monitored (our contribution). (ii) To implement such a system for C. Most embedded software is written in C. Most monitoring tools, however, have been focused on Java. The implementation uses CIL [21], which turns out to be very suited for developing source code instrumentation and runtime monitoring frameworks for C. (iii) To apply RMOR, resulting perhaps most importantly in feed-back from engineers wrt. usability.

The paper is organized as follows. Section 2 gives an overview of the RMOR architecture. Section 3 presents through examples the RMOR specification language. Section 4 summarizes the grammar of the specification language. Section 5 describes implementation details, including principles of the C code that is generated, as well as how the C code is instrumented. Section 6 presents case studies performed with RMOR. Finally Section 7 contains conclusions and outlines future work.

#### 2 Overview of RMOR

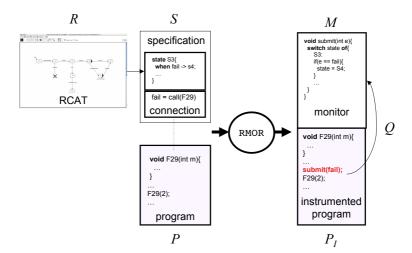

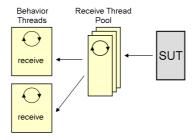

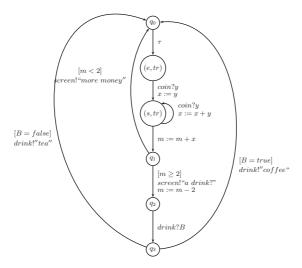

The overall working of RMOR is illustrated in Figure 1. RMOR is a C program transformer, which inputs a pair consisting of a C program and a specification, and which outputs a C program that is "armored" by the specification. The specification is written in a textual format, that either can be programmed directly by a programmer, or it can be generated from a graphical state machine specification in the RCAT specification language. More specifically, RMOR takes as input a specification S in the RMOR specification language, and a C program P and produces a transformed program  $Q = M + P_I$  which is the combination of a monitor M generated from the specification S, and an instrumented version  $P_I$  of P.  $P_I$  is P augmented with additional code that drives the monitor M. Executing the resulting program Q corresponds to executing the original program P, but with the monitor M constantly checking conformance to the specification. In case the specification is violated, an error message is printed on standard output, and in case specified, an error handling function is invoked.

The specification consists of two parts: the behavioral specification expressed as a set of state machines, or monitors as they are called, and an instrumentation specification. The state machines contain states and transitions between states that are triggered by the occurrence of events. Events are just abstract names. The instrumentation part specifies how these abstract event names connect to the code and is the basis for the automated program instrumentation. In the resulting instrumented code  $P_I$ , calls to the monitor M occur as calls of the M\_submit(int event) function. Events are represented as integers. The calls of this function are automatically inserted by RMOR at locations defined by the instrumentation specification. The monitor M itself is a set of synthesized C functions that check conformance to the state machines and which are written into an rmor.c file that has to be compiled and linked together with the application. An rmor h header file is also generated that containts the events and RMOR API prototypes

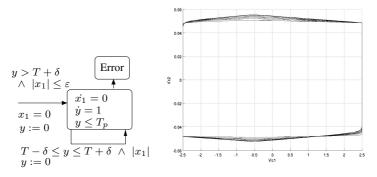

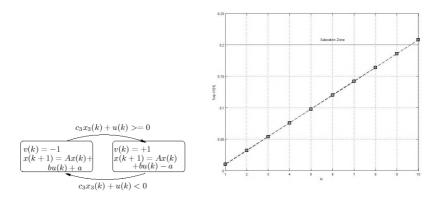

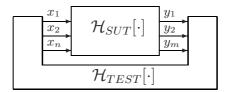

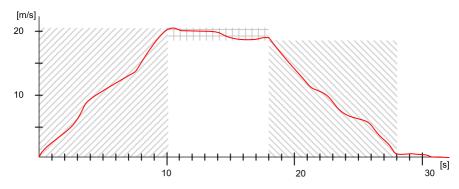

Fig. 1. Overview of RMOR

(function signatures). The header file does not need to be included in the user program under normal circumstances, but can be as explained later in case the user program needs to explicitly refer to monitoring functions. The synthesized monitor uses a fixed amount of memory, hence it does not use dynamic memory allocation.

RMOR is implemented using CIL (C Intermediate Language), a C program analysis and transformation system [21]. CIL is programmed in OCAML, which consequently also is the programming language in which RMOR is implemented. CIL is a high-level representation along with a set of tools that permit easy analysis and source-to-source transformation of C programs. The CIL tool parses a C program and generates an abstract syntax tree annotated with type information. The generated tree represents a program in a clean subset of C. CIL is very robust and has been applied to for example the Linux kernel and GCC's C torture testsuite and processes not only ANSI-C programs but also those using Microsoft C or GNU C extensions. Consequently RMOR inherits the same characteristics. CIL provides a driver which behaves as either the gcc or Microsoft VC compiler and can invoke the preprocessor followed by the CIL application. The advantage of this script is that one can easily use RMOR with existing make files. The RMOR system extends CIL with approximately 2500 lines of code.

# 3 The RMOR State Machine Language

#### 3.1 An Example C Program

In order to illustrate the specification language, consider the following toy application program about which properties will be formulated. The program, located in a file main.c, defines a collection of functions supporting uplink of data from a planetary rover to a space craft<sup>2</sup>:

$<sup>^{\</sup>rm 2}$  The example is fiction and does not represent an existing design.

```

char* header;

Connection open_connection(char* name) {...}

bool close connection (Connection connection) {...}

void cancel transmission(Connection connection) {...}

void write buffer(Connection connection, int data) {...}

void commit buffer(Connection connection) {...}

void acknowledge() {...}

void debug(char* str){...}

main(){

Connection c1,c2;

c1 = open_connection("connection1");

c2 = open_connection("connection2");

write buffer(c1,100);

commit buffer(c1);

close connection(c1);

}

```

The program offers functions for opening and closing a connection between rover and space craft. While the connection is open data can be written to a data buffer, and finally committed, for which an acknowledgment is received and recorded with a call of the function acknowledge. A transmission can also be cancelled, not requiring further action. The program contains a global variable header, containing information about the current connection. The main program illustrates an example scenario.

#### 3.2 Writing a Monitor

RMOR allows to specify properties about the execution order of function calls and global variable accesses. RMOR monitors safety properties, usually formulated as "nothing bad happens", as well as termination-bounded liveness properties "something good eventually happens before program termination". Safety properties are checked each time an event is submitted. Liveness properties are checked at the end of an execution when monitoring is terminated: at that point it is checked whether any outstanding events have not happened that were expected to happen according to the requirements represented by the monitors. In order to illustrate the RMOR notation a set of requirements will be modeled. Consider the following requirements  $R_1$ ,  $R_2$  and  $R_3$  about the call-sequence of the functions in the above API. R<sub>1</sub>: "A connection is opened, accessed zero or more times, and subsequently either closed or canceled. An access is either a write operation or a commit operation";  $R_2$ : "The commit operation must be followed by an acknowledgement before any other operation can be performed, except a cancellation"; R<sub>3</sub>: "It is illegal to have more than one connection opened at any time". These requirements can be formulated as several monitors, for example one for each requirement, or they can be grouped into one monitor as follows.

```

monitor UplinkRequirements {

event OPEN = after call(main.c:open_connection);

```

```

event WRITE = after call(main.c:write buffer);

event COMMIT = after call(main.c:commit buffer);

event ACK = after call(main.c:acknowledge);

event CANCEL = after call(main.c:cancel transmission);

event CLOSE = after call(main.c:close connection);

initial state Closed {

when OPEN -> Opened;

when WRITE | COMMIT | ACK | CLOSE => error;

}

live state Opened {

when COMMIT -> Committing;

when CLOSE -> Closed;

when ACK => error;

}

next state Committing {

when ACK -> Opened;

}

super Active[Opened,Committing]{

when CANCEL -> Closed;

when OPEN => error;

}

}

```

The monitor introduces six events to be monitored and a state machine that any event sequence observed during program execution must conform to. Each event is defined by a predicate, denoting a set of statements in the program that satisfies it (a pointcut using aspect-oriented terminology), and a directive indicating whether the event should emitted before or after any statement satisfying the pointcut. As an example, the event OPEN is associated with the pointcut call (main.c:open\_connection) which is matched by any call of the function open\_connection defined in the file main.c. In the example program there are in fact two such calls. The after directive requires the event to be emitted to the monitor after each of these calls. It is in essence an instruction to RMOR to instrument the code by inserting a call to the monitor after these two calls. Similarly for the other events. Note that following aspect-oriented ideas, the program is oblivious to the fact that it is getting instrumented.

The state machine itself consists of three basic states: Closed, Opened and Committing. Each state is modeled as a named (the name of the state) block enclosed by curly-brackets { ... } containing all its exiting transitions. The Closed state is the initial state, indicated with the *state modifier* keyword initial. In the Closed state, two transitions are defined. The first transition states that the event OPEN brings the monitor into the Opened state. Recall that an OPEN event occurs after any call of the function main.c:open\_connection; The second transition states that if any of the events in the

set {WRITE, COMMIT, ACK, CLOSE} occurs, using the *or*-operator '||', it is it is regarded as an error – error is a special identifier denoting a built-in error state. The double arrow (=>) indicates a transition that leaves a token in the source state, in this case Closed, such that also future violations of this property is detected. Such a transition is called *non-consuming* since it does not consume the source token, as does the normal single arrow *consuming* transition (->). Recall that state machines are non-deterministic.

The Opened state is a *live* state as indicated by the modifier keyword live, meaning that this state must be left before program termination for this specification to be satisfied. This specifically means that either a COMMIT event or a CLOSE event must occur. An ACK event is not allowed to occur in this state. In the Committing state an ACK event must occur as the *next* observable event, indicated by the next state modifier keyword. This has as consequence that no other event can occur, except for a cancellation. The latter exception is a consequence of the super state named Active defined at the end of the monitor. This super state contains the two atomic states Opened and Committing and has two exiting transitions. This is a shorthand for these exiting transitions connected to each substate. The super state definition implies that when in any of the two sub-states it is regarded as an error if an OPEN event occurs, and a CANCEL event brings the monitor back to the initial Closed state.

#### 3.3 Complex Pointcuts

Emissions of events to a monitor are inserted either before or after certain program locations (joinpoints) identified by pointcut expressions occurring after the '=' sign in event definitions. Pointcut expressions can, similar to ASPECTJ and ASPECTC [2], be used directly in event definitions, as we have seen above, or they can be defined and given names in explicit pointcut declarations, using Boolean combinators similar to those used on conditions. The following example illustrates this. Consider the additional requirement R4: "A write operation or an assignment to the header variable (collectively referred to as an update) should be followed by a commit operation before the connection is closed, unless the transmission is cancelled. This, however, only concerns main updates performed in the main.c file, ignoring updates made within any debugging function". In order to capture this requirement RMOR's poincut language is used to define the notion of a main update. The following monitor defines two poincuts, one used to define the other, and an event that is defined in terms of the latter pointcut.

The pointcut Update matches any program statement that is either: (i) is a call of a function defined in main.c and with a name matching the pattern write\*, meaning having the name write as prefix, or (ii) is an update of the variable header declared in

main.c. The file patterns (the part before and including the ':') are optional. Both file names and function/variable names can be indicated as patterns using "\*" to represent any sequence of symbols. The pointcut MainUpdate refines the first pointcut to only concern those program statements occurring in the file main.c but not within any function with a name that contains the string debug. Finally, the event UPDATE is emitted after any main update. Note that this monitor contains no state machine and is purely introduced to define the pointcuts and the event. RMOR allows a monitor to import other monitors to access their pointcuts and events, and the next monitor imports the just presented one to access the UPDATE event, and also imports the original monitor to access further events.

#### 3.4 Error Handling

Our example program violates requirements  $R_2$  (a commit must be followed by an acknowledgment before anything else), and  $R_3$  (no more than one open connection at a time). Running the armored program produced by RMOR therefore causes two error messages to be printed on standard output. It is possible to provide a call-back handler function, which the monitor will call for each violation detected. This function must have the following name and type:

```

void handler(char *monitor, char *state, int kind) {

... user defined code ...

}

```

The first argument indicates the name (a string) of the monitor in which the error was encountered. The second argument indicates the name of the state it occurred in, and finally the third argument indicates the kind of error (a number between 0 and 2): (0) transition into an *error* state, (1) not leaving the *next* state before another event occurs, and (2) terminating in a *live* state. In order for errors to be handled by the handler function, the monitor must be declared with the handled modifier as follows:

```

handled monitor UplinkRequirements {

... as before ...

}

```

#### 4 Elements of the RMOR Grammar

In this subsection elements of the grammar of RMOR are outlined, summarizing the concepts introduced in the example. A specification consists of a sequence of monitors<sup>3</sup>:

An import declaration has the form:

```

<import-decl> ::= "import" <ident> ";"

```

Imports have the sole purpose of giving access to pointcuts and events from other monitors. Imports have no semantics at the state machine level. The grammar rules for pointcut declarations and pointcut expressions are as follows:

```

<pointcut_decl> ::= "pointcut" <ident> "=" <pointcut_expr> ";"

<pointcut_expr> ::=

"call" "(" (<idpat1>":")?<idpat2> ")"

| "set" "(" (<idpat1>":")?<idpat2> ")"

| "within" "(" <idpat1> ")"

| "withincode" "(" (<idpat1>":")?<idpat2> ")"

| <ident>

| <pointcut_expr> "&&" <pointcut_expr>

| <pointcut_expr> "||" <pointcut_expr>

| "!" <pointcut_expr> ")"

<idpat1> ::= ("*" | letter|digit | "_" | "." | "-" | "/" )+

<idpat2> ::= ("*" | letter|digit | "_" )+

```

A poincut expression can specify a function call or a variable assignment, with idpat1 indicating the name of the file in which the called function or updated variable is declared. The within pointcut matches statements occurring in files with names matching the argument, and withincode matches statements occurring within functions with names matching the argument. Beyond this, pointcuts can be referred to by name and conjoined with Boolean operators. An event declaration has one of two forms:

$<sup>^{3}</sup>$  The meta symbol  $^{\star}$  means zero or more occurrences, and ? means zero or one occurrence.

```

<event_decl> ::=

"event" <ident> "=" ("before "|" after") <pointcut_expr> ";"

| "event" <ident> ("," <ident>) ";"

```

The event declarations shown this far are all of the first form. The second form is an abstract event declaration. It just introduces an event name that then can be used in state machines. However, no automated instrumentation is performed and it is the responsibility of the user to manually instrument the program to emit these events using the RMOR API. A state declaration can be of one of two forms:

The first form is the basic state definition: a list of state modifiers, the keyword state, the name of the state, and a list of exiting transitions enclosed in a block. The second form is a super state definition, with the name of the super state and the list of sub-states in between [...] brackets. These sub-states must be defined within the same monitor using the first form of state declaration. It is not possible to use another super state as a sub-state. The super state also has a list of exiting transitions. An anytime state always contains a token, even if an exiting transition is taken (state machines can be non-deterministic). The same effect can be obtained by defining all exiting transitions as non-consuming using the => arrow. A condition is a Boolean expression over event identifiers and the ANY keyword, which in essence represents true, or "any" transition.

In an attempt to offer the possibility of grouping together state machines in one module it has been made possible to define several state machines inside a monitor. Such state machines cannot define any symbols or perform any imports:

```

<machine_decl> ::= "machine" <ident> "{" <state_decl>* "}"

```

RMOR offers in addition an API of functions with which the user application can interact with the monitors. These functions can for example be called from the handler. This includes functions for resetting and stopping monitors, submitting events, and printing monitor status for debugging purposes.

# 5 Implementation

OCAML [22] and its parser modules OCAMLLEX and OCAMLYACC were used to implement the parser for the RMOR specification language. The generated monitors

in C utilize the SGLIB library [23], specifically double-linked lists for implementing sets. The program instrumentation module was, as already mentioned, implemented in OCAML on top of CIL [21].

#### 5.1 Monitor Generation

The lexical scanning of RMOR specifications involves scanning of pointcut expressions, which is a well-known problem in aspect-oriented programming implementations, requiring the lexer to be state oriented, behaving differently in the normal and the pointcut state. OCAMLLEX allows for such state orientation, permitting us to apply a high-level parser generator for the task<sup>4</sup>. The program is parsed into an abstract syntax tree (AST), which is then processed for two purposes: translation of state machines to monitors, and instrumentation of the C code to emit events to the monitors (Section 5.2). The translator that produces state machines takes the AST as input and prints out the monitors in the file rmor.c. There are three constraints that specifically influence how RMOR is implemented: (i) monitors are allowed to be non-deterministic (a consequence for example of the => transition arrow, useful for monitoring), meaning that a state machine can be in more than one state at a given moment; (ii) dynamic memory allocation is not allowed since monitors should be able to monitor embedded flight code as part of a fault protection strategy, where only static memory allocation is allowed; (iii) a future extension of RMOR should allow for events to be parameterized with data values, and hence tokens in states should be able to carry values.

The first constraint requires each transition to produce a **set** of *next states*, computed from the set of *current states*. The second constraint requires that these different sets cannot be allocated dynamically on the fly as new sets are built. Instead, all states are allocated up front, and for each monitor is maintained three collections during next-state computation: a list of *free states*, a set of *current states*, and a set of *next states*. Each collection is modeled as a double-linked list. All states are initially stored in the free list. The monitor subsequently just moves states between these three sets when a new event arrives. At program termination it is checked that no tokens exist in live or next states. The motivation for representing sets as linked lists of records, and not as bitvectors, is the third constraint above, which requires data values to be part of state tokens in an extension of the tool. This will be further discussed in Section 7.

#### 5.2 Instrumentation with CIL

The instrumentation module is implemented using CIL's object oriented visitor pattern framework. RMOR defines a class that subclasses a predefined visitor class, overriding a method for each kind of CIL construct that should be visited. CIL's visiting engine scans depth-first the structure of a CIL program and at each node executes the corresponding method in the user-defined visitor. The code below shows part of the visitor class defined for instrumentation. It overrides the method vinst: instr -> instr list visitAction that is applied to every basic instruction in the C program (essentially function calls and assignment statements, excluding composite statements, such

<sup>&</sup>lt;sup>4</sup> The ASPECTJ parser is for example not constructed using a parser generator.

as loops). This function is expected to return a list of instructions, namely those that the visited instruction is replaced with. The body of the function computes a list of advices to be inserted (advice\_inserts), that if not empty is split into those to be inserted before and after the instruction respectively.

```

class instrumentVisitor = object (self) inherit nopCilVisitor

...

method vinst (i : instr) : instr list visitAction =

...

let advice_inserts = match_instr ... i in

if advice_inserts = [] then

SkipChildren

else

begin

let (before,after) = create_before_after advice_inserts in

ChangeTo (before @ [i] @ after)

end

end

```

The instrumentation consists of inserting calls of the function M\_submit(int event) before or after joinpoints matching the pointcuts associated with events. The function M\_submit stores the submitted event for later reference in the state machines, and subsequently calls the *next-state* function of each state machine.

## 6 Case Study

The Laboratory for Reliable Software at JPL has been developing a RAM File System (RAMFS) for use in future space missions. RAMFS will specifically be used as a backup file system on the next Mars Rover, MSL (Mars Science Laboratory), with launch date September-October 2009. MSL will be the biggest rover yet sent to Mars, and will be three times as heavy and twice the width of the Mars Exploration Rovers (MERs) that landed in 2004. RAMFS implements a thread-safe file system for flight systems in volatile memory (memory that requires a power supply to maintain the stored information). The main purpose of RAMFS is to provide a storage capability that can be used when the disk- or flash-file system is unavailable, e.g., when a spacecraft is in crippled mode, or in case there is not enough disk memory available. It is a project goal to apply various testing and verification technologies to establish confidence in the correctness of this file system [14]. Two different properties were formulated in RMOR and checked against the system. Both properties were satisfied, and malicious manual code modification caused them to be violated as expected.

**Property 1: Matching Semaphore Accesses.** The first property, called MatchSem, checks that semaphore operations are executed correctly: the semaphore must be reserved and released in strictly alternating order. The specification further states that once the semaphore has been reserved, it must eventually be released again. Reserving and releasing the semaphore is performed in the program respectively by calls of functions osal\_sem\_take and osal\_sem\_give. The monitor is defined as follows.

```

monitor MatchSem {

event semtake = before call(osal_sem_take);

event semgive = after call(osal_sem_give);

state Start {

when semtake -> HaveLock;

when semgive -> error;

}

live state HaveLock {

when semgive -> Start;

when semtake -> error;

}

```

Property 2: Protected Memory Updates. While the first property above states that the semaphore is used correctly, the second property states that memory accesses are correctly protected by the semaphore. That is, any access to memory must occur between a semtake and a semgive. Memory accesses come in two forms. The first are updates to the list of free memory through memory allocations with the function ramfs\_alloc\_pages, and memory freeing with the function ramfs\_free\_pages. The second are updates to the memory pages themselves through two functions ramfs\_update\_entry and ramfs\_update\_header. The monitor defines two pointcuts free\_list\_update and page\_update, corresponding to these two kinds of calls.

```

monitor DataProtected {

import MatchSem ;

pointcut free_list_update =

call(ramfs_alloc_pages) || call(ramfs_free_pages);

pointcut page_update =

call(ramfs_update_entry) || call(ramfs_update_header);

event update = before free_list_update || page_update;

state Unsafe {

when semtake -> Safe;

when update -> error;

}

state Safe {

when semgive -> Unsafe;

}

}

```

**Observations.** This case study demonstrated the ease with which a non-expert in RMOR was able to quickly learn the specification language and formulate properties.

Although not seen as a limitation during the exercise, the need for events to carry data values comes to the forefront in this example, specifically when it comes to the first property, that *the semaphore must be reserved and released in strictly alternating order*. The specification should ideally state that for a given semaphore *S*, its acquisition should be followed by a release of this same *S*.

A different case study was performed using RCAT from which RMOR monitors were generated as Büchi automata for an earlier version of RMOR. The case study was a rover controller for the Rocky 8 rover, a research vehicle that is used at JPL to develop, integrate, and demonstrate advanced autonomous robotic capabilities for future Mars missions. Since the specification language used was RCAT and since monitors were generated for an earlier version of RMOR, we shall not provide details about the example or the specifications. It suffices to say that the specification concepts used were similar to those of RMOR, and that the study supported the need for augmenting RMOR with the ability to express time constraints, and the ability to model conditions (predicates) on the state of the C program and use these as guards on transitions.

Concerning efficiency, the overhead naturally depends on the ratio with which monitored function calls and variable accesses are performed in the monitored application compared with the overall computation. Experiments showed that a single monitored call of a function with empty body results in an order of magnitude slow down of that call. Although monitored function calls usually constitute a small fraction of the overall computation, such overhead must be reduced using static analysis and algorithm optimizations.

#### 7 Conclusions and Future Work

The following three aspects are important for acceptance of a technology such as RMOR: (i) convenience of the specification language; (ii) expressiveness of the specification language; (iii) efficiency of monitoring. A contribution of the paper is to illustrate the convenience of a state machine notation in combination with an aspect-oriented pointcut language. Concerning expressive power of the specification language, it currently only offers monitoring of propositional events. The notation should be extended with the ability to parameterize events with data values, corresponding to arguments in monitored functions, timers, and to generally enable C code to occur in the specification, for example allowing C code to be executed as a result of state machine transitions. In current work we are permitting this by directly extending ASPECTC [2] with state machines, utilizing ASPECTC's already existing pointcut language. This work is carried out using the SILVER extensible compiler framework [30]. Future work includes allowing user defined temporal logic operators as shorthands for state machines. Specifically, we plan to allow monitors to be parameterized with pointcuts. This will allow to define temporal operators/specification patterns within the language as is done in the EAGLE specification language [4], permitting very succinct specifications. We are furthermore exploring the possibility of adopting the more expressive rule-based logic RULER [5] as core logic, in which state machines form a special case. Efficiency can be obtained by application of static analysis to reduce code instrumentation.

**Acknowledgements.** Thanks goes to researchers at JPL. Margaret Smith designed the graphical RCAT language, which inspired the design of RMOR. Rajeev Joshi and Matthew Bennett participated in case studies using versions of RMOR. Gerard Holzmann supported the project by funding it as part of NASA's Reliable Software System Development project<sup>5</sup>.

#### References

- Allan, C., Avgustinov, P., Christensen, A.S., Hendren, L., Kuzins, S., Lhoták, O., de Moor, O., Sereni, D., Sittamplan, G., Tibble, J.: Adding Trace Matching with Free Variables to AspectJ. In: OOPSLA 2005, ACM Press, New York (2005)

- 2. AspectC, http://research.msrg.utoronto.ca/ACC

- 3. Ball, T., Rajamani, S.K.: SLIC: a Specification Language for Interface Checking (of C). Technical Report MSR-TR-2001-21, Microsoft Research (2001)

- 4. Barringer, H., Goldberg, A., Havelund, K., Sen, K.: Rule-Based Runtime Verification. In: Steffen, B., Levi, G. (eds.) VMCAI 2004. LNCS, vol. 2937, Springer, Heidelberg (2004)

- Barringer, H., Rydeheard, D., Havelund, K.: Rule Systems for Run-Time Monitoring: from Eagle to RuleR. In: Proc. of the 7th International Workshop on Runtime Verification (RV 2007), Vancouver, Canada. LNCS, vol. 4839, Springer, Heidelberg (2007)

- Bensalem, S., Bozga, M., Krichen, M., Tripakis, S.: Testing Conformance of Real-Time Applications by Automatic Generation of Observers. In: Proc. of the 4th International Workshop on Runtime Verification (RV 2004). ENTCS, vol. 113, Elsevier, Amsterdam (2004)

- 7. Bockisch, C., Mezini, M., Ostermann, K.: Quantifying over Dynamic Properties of Program Execution. In: 2nd Dynamic Aspects Workshop (DAW 2005), Technical Report 05.01. Research Institute for Advanced Computer Science, pp. 71–75 (2005)

- 8. Chen, F., Roşu, G.: MOP: An Efficient and Generic Runtime Verification Framework. In: Object-Oriented Programming, Systems, Languages and Applications (OOPSLA 2007) (2007)

- Douence, R., Fritz, T., Loriant, N., Menaud, J.-M., Sgura-Devillechaise, M., Südholt, M.: An Expressive Aspect Language for System Applications with Arachne. In: Proc. of the 4th international conference on Aspect-oriented software development, Chicago, USA, ACM Press, New York (2005)

- Drusinsky, D.: Semantics and Runtime Monitoring of TLCharts: Statechart Automata with Temporal Logic Conditioned Transitions. In: Proc. of the 4th International Workshop on Runtime Verification (RV 2004), Barcelona, Spain. ENTCS, vol. 113, Elsevier, Amsterdam (2004)

- 11. Drusinsky, D.: Modeling and Verification using UML Statecharts, p. 400. Elsevier, Amsterdam (2006)

- Eckmann, S., Vigna, G., Kemmerer, R.A.: STATL Definition. Reliable Software Group, Department of Computer Science, University of California, Santa Barbara, CA 93106 (2001)

- 13. Finkbeiner, B., Sipma, H.: Checking Finite Traces using Alternating Automata. In: Proc. of the 1st International Workshop on Runtime Verification (RV 2001). ENTCS, vol. 55(2), Elsevier, Amsterdam (2001)

- Groce, A., Joshi, R.: Extending Model Checking with Dynamic Analysis. In: Logozzo, F., Peled, D., Zuck, L. (eds.) Proc. of Ninth International VMCAI conference (VMCAI 2008). LNCS, Springer, Heidelberg (2008)

<sup>&</sup>lt;sup>5</sup> Part of the work described in this paper was carried out at the Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration. Part of the work was carried out at Kestrel Technology, under a contract with the National Aeronautics and Space Administration.

- 15. Havelund, K., Roşu, G.: An Overview of the Runtime Verification Tool Java PathExplorer. Formal Methods in System Design 24(2) (March 2004)

- Havelund, K., Roşu, G.: Efficient Monitoring of Safety Properties. Software Tools for Technology Transfer 6(2), 158–173 (2004)

- 17. Holzmann, G.J.: The SPIN Model Checker, Primer and Reference Manual. Addison-Wesley, Reading (2004)

- Kiczales, G., Hilsdale, E., Hugunin, J., Kersten, M., Palm, J., Griswold, W.G.: An Overview of AspectJ. In: Knudsen, J.L. (ed.) ECOOP 2001. LNCS, vol. 2072, pp. 327–353. Springer, Heidelberg (2001)

- 19. Kim, M., Kannan, S., Lee, I., Sokolsky, O.: Java-MaC: a Run-time Assurance Tool for Java. In: Proc. of the 1st International Workshop on Runtime Verification (RV 2001). ENTCS, vol. 55(2), Elsevier, Amsterdam (2001)

- Martin, M., Livshits, B., Lam, M.S.: Finding Application Errors using PQL: a Program Query Language. In: Proc. of the 20th Annual ACM SIGPLAN Conference on Object-Oriented Programming, Systems, Languages and Applications, ACM Press, New York (2005)

- Necula, G.C., McPeak, S., Rahul, S.P., Weimer, W.: CIL: Intermediate Language and Tools for Analysis and Transformation of C Programs. In: Proc. of Conference on Compilier Construction (2002)

- 22. OCAML, http://caml.inria.fr/index.en.html

- 23. SGLIB. A Simple Generic Library for C, http://sglib.sourceforge.net

- 24. Smith, M.: Requirements for the Demonstration Version of the Requirements Capture Tool (RCAT). JPL/RSS Technical Report, RSS Document Number: ESS-02-001 (2005)

- Smith, M., Havelund, K.: Requirements Capture with RCAT. Jet Propulsion Laboratory, California Institute of Technology (submitted for publication, February 2008)

- Stolz, V., Bodden, E.: Temporal Assertions using AspectJ. In: Proc. of the 5th International Workshop on Runtime Verification (RV 2005). ENTCS, vol. 144(4), Elsevier, Amsterdam (2005)

- 27. T-UPPAAL, http://www.cs.aau.dk/~marius/tuppaal

- Vanderperren, W., Suvé, D., Augustina Cibrán, M., De Fraine, B.: Stateful Aspects in JAsCo. In: Gschwind, T., Aßmann, U., Nierstrasz, O. (eds.) SC 2005. LNCS, vol. 3628, Springer, Heidelberg (2005)

- Walker, R., Viggers, K.: Implementing Protocols via Declarative Event Patterns. In: Taylor, R.N., Dwyer, M.B. (eds.) ACM Sigsoft 12th International Symposium on Foundations of Software Engineering (FSE-12), pp. 159–169. ACM Press, New York (2004)

- Wyk, E.V., Bodin, D., Gao, J., Krishnan, L.: Silver: an Extensible Attribute Grammar System.

In: Workshop on Language Descriptions, Tools, and Applications (2007)

# Test Construction for Mathematical Functions<sup>\*</sup>

#### Victor Kuliamin

Institute for System Programming

Russian Academy of Sciences

109004, B. Kommunistitcheskaya, 25, Moscow, Russia

kuliamin@ispras.ru

**Abstract.** The article deals with problems of testing implementations of mathematical functions working with floating-point numbers. It considers current standards' requirements to such implementations and demonstrates that those requirements are not sufficient for correct operation of modern systems using sophisticated mathematical modeling. Correct rounding requirement is suggested to guarantee preservation of all important properties of implemented functions and to support high level of interoperability between different mathematical libraries and modeling software using them. Test construction method is proposed for conformance test development for current standards supplemented with correct rounding requirement. The idea of the method is to use three different sources of test data: floating-point numbers satisfying specific patterns, boundaries of intervals of uniform function behavior, and points where correct rounding requires much higher precision than in average. Some practical results obtained by using the method proposed are also presented.

#### 1 Introduction

In modern world computers help to visualize and understand behavior of very complex systems. Confirmation of this behavior with the help of real experiments is too expensive and often even impossible. To ensure correct results of such modeling we need to have adequate models and correctly working modeling systems. Constructing adequate models is very interesting problem, which, unfortunately, cannot be considered in this article in detail. The article concerns the second part – how to ensure correct operation of modeling systems. Such systems often use very sophisticated and peculiar algorithms, but in most cases they need for work basic mathematical functions implemented in software libraries or in hardware.

So, mathematical libraries are common components of most modeling software and correct operation of the latter cannot be achieved without correct implementation of basic functions by the former. In practice software quality is controlled and assured mostly with the help of testing, but testing of mathematical libraries usually is organized using simplistic ad hoc approaches and random

$<sup>^\</sup>star$  This work is partially supported by RFBR grants 05-01-0099a, 06-07-89261a, and by contract 02.467.11.1006 with Russian Federal Science and Innovation Agency.

K. Suzuki et al. (Eds.): TestCom/FATES 2008, LNCS 5047, pp. 23–37, 2008.

<sup>©</sup> IFIP International Federation for Information Processing 2008

test data generation. Specifics of floating-point calculations makes construction of both correct and efficient implementations of functions, along with testing that they are actually correct, a nontrivial task. The main goal of this paper is to present a systematic method of test construction for mathematical functions implemented in software or hardware on the base of floating-point arithmetic stated in IEEE 754 standard [1].

The main ideas of the method proposed are to check correct rounding requirement and to combine three different sources of test data, which are targeted to catch common errors made by implementors of mathematical libraries.

- Floating-point (FP) numbers of specific structure. They include both boundary numbers like the greatest FP number (within certain precision), the smallest normalized number, etc., and numbers, which binary representations satisfy some specific patterns. In addition the closest floating-point numbers to the values of the reverse function in such points are calculated and also used as testing points for the direct function. Roughly speaking, a function is tested on points where its argument or its value are on the boundary or satisfy one of the chosen patterns.

- Boundaries of intervals, where the function under test behaves in uniform way. Several points on each of those intervals are also added to the test suite.

Detailed rules for determining such intervals are presented below.

- Floating-point numbers, for which correct rounding of the function value requires much higher precision of calculations than average. These points are rather hard to seek and some methods for their search are presented in the section on test construction method.

The contribution of this article is the systematic description of the approach proposed, much more clear and concise then it was done in the paper [2] describing the starting phase of the underlying work. In addition this paper describes methods for searching FP numbers, for which correct rounding of the function value is hard, including the new one, the integer secants method. This research was started during the OLVER project [3] on formalization of LSB [4] standard requirements and conformance test development.

Before presenting the test construction method itself it is useful to recall some details of FP arithmetic, which are necessary for understanding details of the method. To make tests practically useful we also should clearly understand what precise requirements should be checked. So, the next section presents review of existing standards concerning mathematical functions working with FP numbers and analysis of these standards' requirements.

# 2 Standards' Requirements

To be able to check implementation of a function we should know how it should behave. Practically significant requirements on the behavior of functions on FP numbers can be found in several standards.

- Standards IEEE 754 [1] (also known as IEC 60559 [5]) and IEEE 854 [6] define representation of FP numbers, rounding modes, also describe basic arithmetic operations, comparisons, type conversions, square root function, and floating-point remainder.

- Standards ISO C [7] and POSIX [8] impose additional requirements on about 40 functions of real and complex variable implemented in standard C library.

- Standard ISO/IEC 10697 [9,10,11] gives more elaborated and precise set of requirements for elementary functions.

#### 2.1 Floating-Point Numbers

Standards IEEE 754 and IEEE 854 define FP numbers based on various radices. Further exposition concerns only binary numbers, because other radices are used in practice rarely. Nevertheless, all the techniques presented can be extended to FP numbers with different radix, if it is necessary.

Representation of binary FP numbers is defined by two main parameters – n, the number of bits in the representation, and k < n, the number of bits used to represent an exponent. The interpretation of different bits is presented below.

- The first bit represents the sign of a number.

- The next k bits from the 2-nd to the k+1-th represent the exponent of a number.

- All the rest bits from k+2—th to n—th represent the mantissa or the significand of a number.

A number X with the sign bit S, the exponent E, and the mantissa M is expressed in the following way.

- 1. If E>0 and  $E<2^k-1$  then X is called normalized and is calculated with the formula  $X=(-1)^S2^{(E-2^{k-1}+1)}(1+M/2^{n-k-1})$ . Actual exponent is shifted to make possible representation of both large and small numbers. The last part of the formula is simply 1 followed by point and mantissa bits as the binary representation of X without exponent.

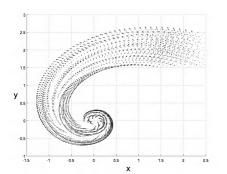

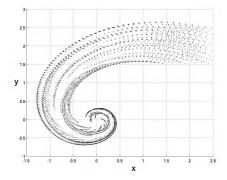

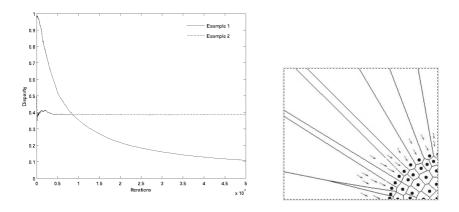

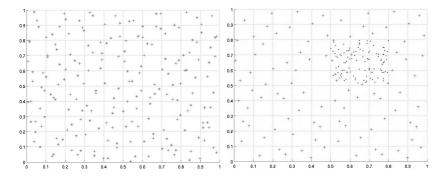

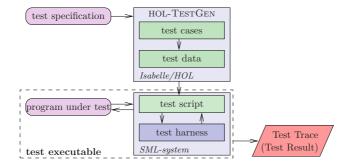

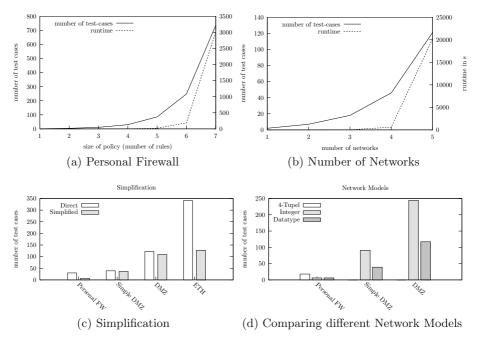

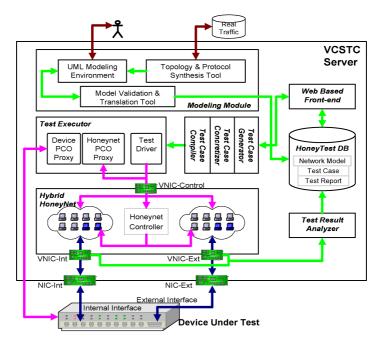

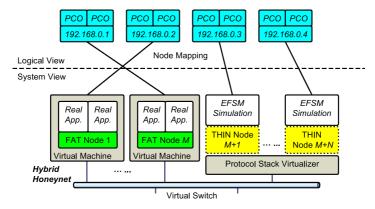

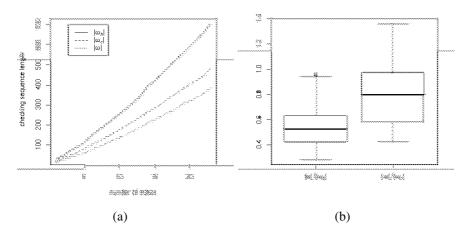

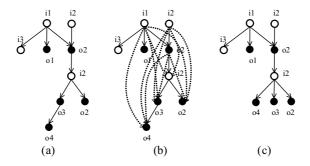

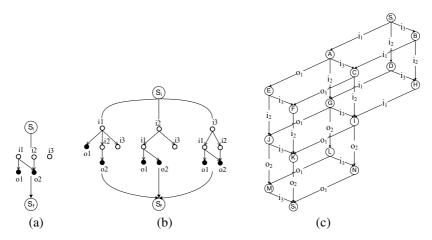

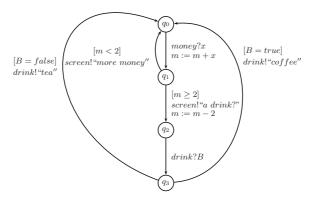

- 2. If E = 0 then X is called denormalized and is computed according to another formula  $X = (-1)^S 2^{(-2^{k-1}+2)} (M/2^{n-k-1})$ . Here mantissa bits follow 0 and the point. Note also, that this gives two zero values +0 and -0.